TECHNISCHE UNIVERSITÄT ILMENAU Institut für Praktische Informatik und Medieninformatik Fakultät für Informatik und Automatisierung Fachgebiet Datenbanken und Informationssysteme

Dissertation

# Finding the Right Processor for the Job — Co-Processors in a DBMS

vorgelegt von

Dipl.-Inf. Hannes Rauhe

geboren am 5.9.1985 in Meiningen

zur Erlangung des akademischen Grades

Dr.-Ing.

1. Gutachter: Prof. Dr.-Ing. habil. Kai-Uwe Sattler

2. Gutachter: Prof. Dr.-Ing. Wolfgang Lehner

3. Gutachter: Prof. Dr. Guido Moerkotte

urn:nbn:de:gbv:ilm1-2014000240

Ilmenau, den 19. Oktober 2014

# Abstract

Today, more and more Database Management Systems (DBMSs) keep the data completely in memory during processing or even store the entire database there for fast access. In such system more algorithms are limited by the capacity of the processor, because the bottleneck of Input/Output (I/O) to disk vanished. At the same time Graphics Processing Units (GPUs) have exceeded the Central Processing Unit (CPU) in terms of processing power. Research has shown that they can be used not only for graphic processing but also to solve problems of other domains. However, not every algorithm can be ported to the GPU's architecture with benefit. First, algorithms have to be adapted to allow for parallel processing in a Single Instruction Multiple Data (SIMD) style. Second, there is a transfer bottleneck because high performance GPUs are connected via PCI-Express (PCIe) bus.

In this work we explore which tasks can be offloaded to the GPU with benefit. We show, that query optimization, query execution and application logic can be sped up under certain circumstances, but also that not every task is suitable for offloading. By giving a detailed description, implementation, and evaluation of four different examples, we explain how suitable tasks can be identified and ported.

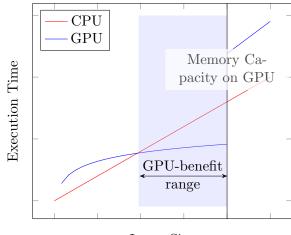

Nevertheless, if there is not enough data to distribute a task over all available cores on the GPU it makes no sense to use it. Also, if the input data or the data generate during processing does not fit into the GPU's memory, it is likely that the CPU produces a result faster. Hence, the decision which processing unit to use has to be made at run-time. It is depending on the available implementations, the hardware, the input parameters and the input data. We present a self-tuning approach that continually learns which device to use and automatically chooses the right one for every execution.

# Abbreviations

- **AES** Advanced Encryption Standard

- $\boldsymbol{\mathsf{AVX}}$  Advanced Vector Extensions

- **BAT** Binary Association Table

**BLAS** Basic Linear Algebra Subprograms

**CPU** Central Processing Unit

$\ensuremath{\mathsf{CSV}}$  Comma Separated Values

**DBMS** Database Management System

**DCM** Decomposed Storage Model

**ETL** Extract, Transform, Load

**FLOPS** Floating Point Operations per Second

FPGA Field-Programmable Gate Array

**FPU** Floating Processing Unit

**GPU** Graphics Processing Unit

${\ensuremath{\mathsf{GPGPU}}}$  General Purpose Graphics Processing Unit

$\ensuremath{\mathsf{HDD}}$  Hard Disk Drive

I/O Input/Output

$\ensuremath{\mathsf{JIT}}$ Just-In-Time

LWC Light-Weight Compression

**MMDBMS** Main Memory Database System

**ME** Maximum Entropy

**MIC** Many Integrated Core

**MVS** Multivariant Statistics

**NOP** No Operation

- **ODBC** Open Database Connectivity

- **OLTP** Online Transactional Processing

- **OLAP** Online Analytical Processing

- ${\sf ONC}$  Open-Next-Close

- $\boldsymbol{\mathsf{OS}}$  Operating System

- **PCIe** PCI-Express

- **PPE** PowerPC Processing Element

- **QEP** Query Execution Plan

- $\ensuremath{\mathsf{QPI}}$  Intel QuickPath Interconnect

- **RAM** Random Access Memory

- **RDBMS** Relational Database Management System

- **RDMA** Remote Direct Memory Access

- **SIMD** Single Instruction Multiple Data

- ${\sf SMX}$ Streaming Multi Processor

- **SPE** Synergistic Processing Element

- SQL Structured Query Language

- ${\ensuremath{\mathsf{SSD}}}$  Solid State Drive

- $\ensuremath{\mathsf{SSE}}$  Streaming SIMD Extensions

- ${\sf STL}$ Standard Template Library

- **TBB** Intel's Thread Building Blocks

- ${\sf UDF}$  User-Defined Function

- **UVA** Universal Virtual Addressing

# Contents

| 1. | Intro | oductio |                                                                                                                                                       | 1  |  |  |  |  |  |

|----|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

|    | 1.1.  | Motiva  | ation                                                                                                                                                 | 1  |  |  |  |  |  |

|    | 1.2.  | Contri  | butions                                                                                                                                               | 2  |  |  |  |  |  |

|    | 1.3.  | Outlin  | e                                                                                                                                                     | 4  |  |  |  |  |  |

| 2. | Mai   | n Mem   | ory Database Management Systems                                                                                                                       | 5  |  |  |  |  |  |

|    | 2.1.  | OLTP    | and OLAP                                                                                                                                              | 5  |  |  |  |  |  |

|    | 2.2.  | Main I  | Memory DBMS for a Mixed Workload                                                                                                                      | 7  |  |  |  |  |  |

|    |       | 2.2.1.  | SAP HANA Architecture                                                                                                                                 | 8  |  |  |  |  |  |

|    |       | 2.2.2.  | Columnar Storage                                                                                                                                      | 10 |  |  |  |  |  |

|    |       | 2.2.3.  | Compression                                                                                                                                           | 11 |  |  |  |  |  |

|    |       | 2.2.4.  | Main and Delta Storage                                                                                                                                | 16 |  |  |  |  |  |

|    | 2.3.  | Relate  | d Work: Using Co-processors in a DBMS                                                                                                                 | 17 |  |  |  |  |  |

| 3. | GPL   | Js as C | o-Processors                                                                                                                                          | 19 |  |  |  |  |  |

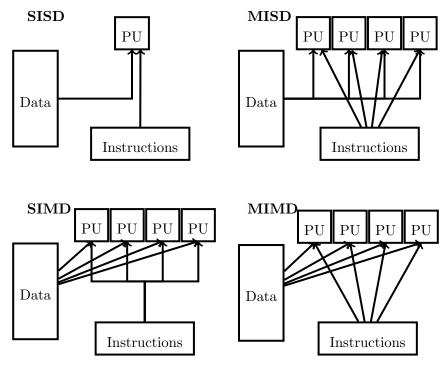

|    | 3.1.  | SIMD    | Processing and Beyond                                                                                                                                 | 19 |  |  |  |  |  |

|    |       | 3.1.1.  | Flynn's Taxonomy                                                                                                                                      | 20 |  |  |  |  |  |

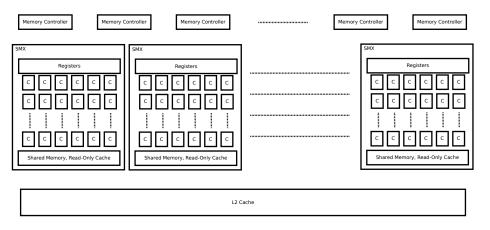

|    |       | 3.1.2.  | Hierarchy of Parallelism—the GPU Architecture                                                                                                         | 21 |  |  |  |  |  |

|    |       | 3.1.3.  | Programming Model for GPU Parallelsim                                                                                                                 | 22 |  |  |  |  |  |

|    | 3.2.  | Comm    | unication between CPU and GPU                                                                                                                         | 23 |  |  |  |  |  |

|    | 3.3.  |         |                                                                                                                                                       |    |  |  |  |  |  |

|    | 3.4.  | Micro-  | Benchmarks                                                                                                                                            | 26 |  |  |  |  |  |

|    |       | 3.4.1.  |                                                                                                                                                       | 26 |  |  |  |  |  |

|    |       | 3.4.2.  | Single Core Performance                                                                                                                               | 28 |  |  |  |  |  |

|    |       | 3.4.3.  | Streaming                                                                                                                                             | 29 |  |  |  |  |  |

|    |       | 3.4.4.  | Matrix Multiplication                                                                                                                                 | 32 |  |  |  |  |  |

|    |       | 3.4.5.  | String Processing                                                                                                                                     | 33 |  |  |  |  |  |

|    | 3.5.  | DBMS    | Functionality on GPUs                                                                                                                                 | 37 |  |  |  |  |  |

|    |       | 3.5.1.  | Integrating the GPU for Static Tasks into the DBMS                                                                                                    | 39 |  |  |  |  |  |

|    |       | 3.5.2.  | Re-Designing Dynamic Tasks for Co-Processors                                                                                                          | 41 |  |  |  |  |  |

|    |       | 3.5.3.  | Scheduling                                                                                                                                            | 42 |  |  |  |  |  |

| 4. | Inte  | grating | Static GPU Tasks Into a DBMS                                                                                                                          | 43 |  |  |  |  |  |

|    | 4.1.  | GPU     | Utilization with Application Logic                                                                                                                    | 44 |  |  |  |  |  |

|    |       | 4.1.1.  | External Functions in IBM DB2                                                                                                                         | 44 |  |  |  |  |  |

|    |       | 4.1.2.  | K-Means as UDF on the GPU                                                                                                                             | 45 |  |  |  |  |  |

|    |       | 4.1.3.  | $Implementation \ldots \ldots$ | 46 |  |  |  |  |  |

|    |       |         |                                                                                                                                                       |    |  |  |  |  |  |

| <ul> <li>4.1.5. Conclusion</li></ul>                                                                                                                                                                                                                                |         |         | ·<br>·<br>·<br>· | · · · · · · · · · · · · · · · · · · · | · · ·<br>· · ·<br>· · · | 52<br>52<br>53<br>54<br>55<br>56<br>57<br>57 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|------------------|---------------------------------------|-------------------------|----------------------------------------------|

| <ul> <li>4.2.1. Selectivity Estimations and Join Paths</li></ul>                                                                                                                                                                                                    |         |         | ·<br>·<br>·<br>· | - · ·                                 | · · ·<br>· · ·<br>· · · | 52<br>53<br>54<br>55<br>56<br>57<br>57       |

| <ul> <li>4.2.1. Selectivity Estimations and Join Paths</li></ul>                                                                                                                                                                                                    |         |         | ·<br>·<br>·<br>· | - · ·                                 | · · ·<br>· · ·<br>· · · | 52<br>53<br>54<br>55<br>56<br>57<br>57       |

| <ul> <li>4.2.2. Maximum Entropy for Selectivity Estimations</li> <li>4.2.3. Implementation of the the Newton Method</li> <li>4.2.4. Evaluation</li></ul>                                                                                                            | sts     |         | ·<br>·<br>·<br>· | - · ·                                 | · ·<br>· ·<br>· ·       | 53<br>54<br>55<br>56<br>57<br>57             |

| <ul> <li>4.2.3. Implementation of the the Newton Method</li></ul>                                                                                                                                                                                                   | sts     | · · · · |                  | • •                                   | · ·<br>· ·<br>· ·       | 54<br>55<br>56<br>57<br>57                   |

| <ul> <li>4.2.5. Conclusion</li></ul>                                                                                                                                                                                                                                |         | · · ·   |                  | • •                                   | <br><br>                | 56<br>57<br>57                               |

| <ul> <li>4.2.5. Conclusion</li></ul>                                                                                                                                                                                                                                |         | · · ·   |                  | • •                                   | <br><br>                | 56<br>57<br>57                               |

| <ul> <li>4.3.1. Implementation</li></ul>                                                                                                                                                                                                                            | · · · · |         |                  | •                                     | <br>                    | 57                                           |

| <ul> <li>4.3.1. Implementation</li></ul>                                                                                                                                                                                                                            | · · · · |         |                  | •                                     | <br>                    | 57                                           |

| <ul> <li>4.3.3. Conclusion</li></ul>                                                                                                                                                                                                                                |         |         |                  |                                       |                         |                                              |

| <ul> <li>4.4. Related Work</li></ul>                                                                                                                                                                                                                                |         |         |                  |                                       |                         | 61                                           |

| <ul> <li>5. Query Execution on GPUs—A Dynamic Task</li> <li>5.1. In General: Using GPUs for data-intensive problems</li> <li>5.2. JIT Compilation—a New Approach suited for the GPU</li> </ul>                                                                      |         | •••     |                  |                                       |                         | 62                                           |

| 5.1. In General: Using GPUs for data-intensive problems 5.2. JIT Compilation—a New Approach suited for the GPU                                                                                                                                                      |         |         |                  |                                       |                         | 62                                           |

| 5.1. In General: Using GPUs for data-intensive problems 5.2. JIT Compilation—a New Approach suited for the GPU                                                                                                                                                      |         |         |                  |                                       |                         |                                              |

| 5.2. JIT Compilation—a New Approach suited for the GPU $\therefore$                                                                                                                                                                                                 |         |         |                  |                                       |                         | 65                                           |

| * **                                                                                                                                                                                                                                                                |         |         |                  |                                       |                         |                                              |

| 5.3. A Model for Parallel Query Execution                                                                                                                                                                                                                           |         |         |                  |                                       |                         |                                              |

|                                                                                                                                                                                                                                                                     |         |         |                  |                                       |                         |                                              |

| 5.4. Extending the Model for GPU Execution                                                                                                                                                                                                                          |         |         |                  |                                       |                         |                                              |

| 5.4.1. Concrete Example                                                                                                                                                                                                                                             |         |         |                  |                                       |                         |                                              |

| 5.4.2. Limitations of the GPU Execution                                                                                                                                                                                                                             |         |         |                  |                                       |                         |                                              |

| 5.5. Evaluation                                                                                                                                                                                                                                                     |         |         |                  |                                       |                         |                                              |

| 5.5.1. Details on Data Structures                                                                                                                                                                                                                                   |         |         |                  |                                       |                         |                                              |

| 5.5.2. Test System and Test Data                                                                                                                                                                                                                                    |         |         |                  |                                       |                         |                                              |

| 5.5.3. GPU and CPU Performance                                                                                                                                                                                                                                      |         |         |                  |                                       |                         |                                              |

| 5.5.4. Number of Workgroups and Threads                                                                                                                                                                                                                             |         |         |                  |                                       |                         |                                              |

| 5.5.5. The Overhead for Using the GPU                                                                                                                                                                                                                               |         |         |                  |                                       |                         |                                              |

| 5.6. Related Work                                                                                                                                                                                                                                                   |         |         |                  |                                       |                         |                                              |

| 5.7. Conclusion                                                                                                                                                                                                                                                     | •••     | • •     | •                | •                                     |                         | 81                                           |

| 6. Automatically Choosing the Processing Unit                                                                                                                                                                                                                       |         |         |                  |                                       |                         | 83                                           |

| 6.1. Motivation                                                                                                                                                                                                                                                     |         |         |                  |                                       |                         |                                              |

| 6.2. Operator Model                                                                                                                                                                                                                                                 |         |         |                  |                                       |                         |                                              |

| 6.2.1. Base Model                                                                                                                                                                                                                                                   |         |         |                  |                                       |                         |                                              |

|                                                                                                                                                                                                                                                                     |         |         |                  |                                       |                         |                                              |

| 6.2.2. Restrictions                                                                                                                                                                                                                                                 |         |         |                  |                                       |                         |                                              |

| 6.2.2. Restrictions                                                                                                                                                                                                                                                 |         |         |                  |                                       |                         |                                              |

| 6.3. Decision Model                                                                                                                                                                                                                                                 |         |         | •                | •                                     |                         | 88                                           |

| 6.3. Decision Model         6.3.1. Problem Definition                                                                                                                                                                                                               |         |         |                  |                                       |                         |                                              |

| 6.3. Decision Model       6.3.1.         6.3.1. Problem Definition       6.3.2.         6.3.2. Training and Execution Phase       6.3.2.                                                                                                                            | <br>    |         |                  |                                       |                         | 89                                           |

| <ul> <li>6.3. Decision Model</li></ul>                                                                                                                                                                                                                              | · · ·   | •••     | •                | •                                     | <br>                    | $\frac{89}{91}$                              |

| 6.3. Decision Model       6.3.1. Problem Definition         6.3.1. Problem Definition       6.3.2. Training and Execution Phase         6.3.3. Model Deployment       6.3.3. Model Deployment         6.4. Evaluation       6.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1 | · · · · | •••     |                  | •                                     | <br><br>                | 89<br>91<br>92                               |

| <ul> <li>6.3. Decision Model</li></ul>                                                                                                                                                                                                                              | · · · · | · · ·   |                  | •                                     | · ·<br>· ·              | 89<br>91<br>92<br>92                         |

| <ul> <li>6.3. Decision Model</li></ul>                                                                                                                                                                                                                              | · · · · | · · ·   |                  | •                                     | <br><br><br>            | 89<br>91<br>92<br>92<br>95                   |

### Contents

|              | 6.5. Related Work                  |  |  |  |     |  |

|--------------|------------------------------------|--|--|--|-----|--|

| 7.           | 7. Conclusion                      |  |  |  |     |  |

| Bibliography |                                    |  |  |  |     |  |

| Α.           | Appendix                           |  |  |  | 113 |  |

|              | A.1. Hardware Used for Evaluations |  |  |  | 113 |  |

# 1. Introduction

In the 1970s the idea of a database machine was a trending topic in research. The hardware of these machines was supposed to be built from ground up to serve only one purpose: efficiently accessing and processing data stored in a Database Management System (DBMS). One of the common ideas of the different designs proposed was the usage of a high number of processing units in parallel. The evolution of the Central Processing Unit (CPU) and disks overtook the development of these database machines and in the 80s, the idea was declared a failure [11]. Thirty years later researchers again proposed to use a massively parallel architecture for data processing, but this time, it was already available: the Graphics Processing Unit (GPU). However, except for some research systems there is still no major DBMS that runs on GPUs.

We think that the reason for this is the versatility of modern DBMS. An architecture for DBMS must be able to do every task possible reasonably well, whether it is aggregating data, simple filtering, processing transactions, complex mathematical operations, or the collection and evaluation of statistics on the data stored in the system. A specialized processor may be able to do a subset of these tasks very fast, but then it will fail to do the rest. The GPU is able to process a huge amount of data in parallel, but it has problems with short transactions, which are not suitable for parallel processing, because they require a consistent view on the data.

However, nowadays different processing units are available in one system. In recent research therefore the focus switched to the usage of heterogeneous hardware and the concept of co-processing. Instead of calculating all by itself, the CPU orchestrates a number of different processing units within the system and decides for each task, where to execute it. The question therefore not longer is: "How does the perfect processor for a DBMS look?", but

"Which of the available processor is the right one to use for a certain task?".

### 1.1. Motivation

On the one hand there are many different tasks a DBMS has to process to store data and keep it accessible. There are the operators used for query execution, such as selection, join, and aggregation with simple or complex predicates. Under the hood the systems executes much more logic to maintain stored data and collect meta data on how users access the content. These statistics are used to optimize the query execution; partly with complex mathematical methods. Additionally, most vendors position their DBMS more and more as a data management platform that is not only able to execute queries but any application logic defined by the user as well.

#### 1. Introduction

On the other hand every standard PC can be equipped with powerful co-processors, specialized on a certain domain of algorithms. Almost any modern PC already has a GPU which is able to solve general purpose algorithms with the help of its massively parallel architecture. Additionally, there are Field-Programmable Gate Arrays (FPGAs), Intel's Xeon Phi, or IBM's Cell processor. Of course, any task can be solved by the CPU, but since its purpose is so generic, other hardware may be

- cheaper,

- more efficient in terms of memory consumption,

- or simply faster

at executing the task. Even if the co-processor is just as good as the CPU for a certain problem; if it is available in the system anyhow it can be used to free resources on the CPU for other jobs.

However, in contrast to co-processors that are integrated into the CPU—such as the Floating Processing Unit (FPU) or cryptography processors, e.g., for accelerating Advanced Encryption Standard (AES)–the co-processors mentioned in the last paragraph cannot be used by just re-compiling the code with special instructions. Instead, they require their own programming model and special compilers. That means that most algorithms have to be re-written to run on co-processors. This re-write is not trivial, because especially GPU algorithms require a completely different approach. Since the prediction of the performance of those new algorithm is impossible due to the complexity of the hardware, there are three questions to answer:

- Which tasks can be ported to a co-processor and how is this done?

- Which tasks are likely and which are unlikely to benefit from another architecture?

- How can the system automatically decide on the best processing unit to use for a specific task?

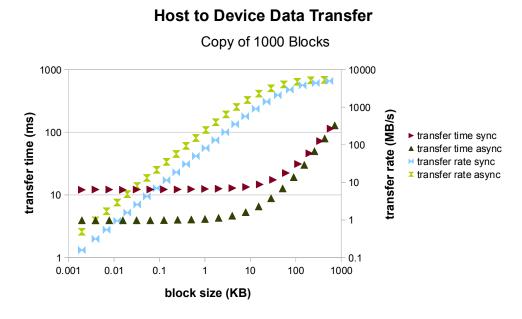

At the moment, the data to be processed by a task usually has to be copied to the co-processor, so data-intensive tasks are usually unlikely to benefit from the GPU.

However, since we reached a peak of single-thread CPU performance because of physics [57], CPU vendors are changing their architectures to support for instance vectorized and multi-threaded execution. These concepts are already built to an extreme in GPUs and FPGAs. In heterogeneous architectures, GPUs are integrated into the CPU, e.g., AMD's Fusion architecture [14]. Hence, modifications to simple algorithms or completely new algorithms for co-processor architectures will play a key role in the future for CPU development as well.

## 1.2. Contributions

In this thesis we take a deep look into using the GPU as co-processor for DBMS operations. We compare the architecture and explain, where the GPU is good at and when it is better to use the CPU. By doing a series of micro benchmarks we compare the performance of a GPU to typical server CPUs. Against popular opinion the GPU is not necessarily always better for parallel compute-intensive algorithms. Modern server CPUs provide a parallel architecture with up to 8 powerful cores themselves. With the help of the benchmarks we point out a few rules of thumb to identify good candidates for GPU execution.

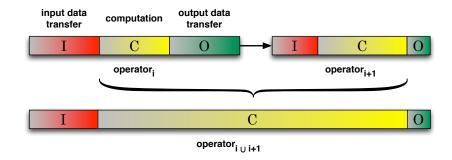

The reason that the GPU provides so much raw power is that hundreds of cores are fitted onto one board. These cores are simple and orders of magnitude slower than a typical CPU core and because of their simplicity they do not optimize the execution of instructions. Where the CPU uses branch-prediction and out-of-order-execution, on the GPU each instruction specifies what one core does and when. Additionally porting an algorithm to the Single Instruction Multiple Data (SIMD) execution model often involves overhead. Missing optimization and the necessary overhead usually mean that only a fraction of the theoretical power can actually be used. Hence the code itself has to be highly optimized for the task. Because of this we have to differentiate between static tasks that always execute the same code branches in the same order, and dynamic tasks such as query execution, where modular code blocks are chained and executed depending on the query.

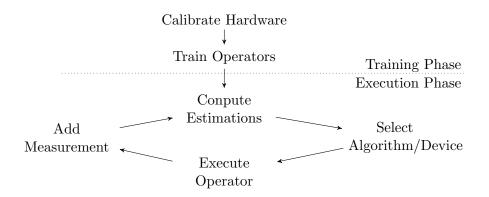

For static tasks we show candidates from three different classes: application logic, query optimization, and a maintenance task. While the first two can benefit from the GPU for certain input parameters, the maintenance task is not only data-intensive but also not "compatible" to the GPU's architecture. For dynamic tasks we propose code generation and Just-In-Time (JIT)-compilation to let the compiler optimize the code for the specific use case at run-time. In any case: if the input for a task is too small, not all cores on the GPU can be used and performance is lost. Hence, we have to decide each time depending on the input whether it is worth using the GPU for the job. In the last part of this thesis we present a framework which automatically makes a decision based on predicted run-times for the execution.

We show that

- there is a huge difference between parallel algorithms for the CPU and the GPU.

- application logic can be executed by the DBMS and on the GPU with advantages from both concepts.

- query optimization can benefit from the performance the GPU provides in combination with a library for linear algebra.

- there are tasks that simply cannot benefit from the GPU; either because they are data intensive or because they are just not compatible to the architecture.

- we can execute queries completely on the GPU, but there are limits for what can be done with our approach.

- the system can learn, when using the co-processor for a certain task is beneficial and automatically decide, where to execute a task.

#### 1. Introduction

In every evaluation we aim for a fair comparison between algorithms optimized for and running on a modern multi-core CPU against GPU-optimized algorithms. Because DBMS usually run on server hardware, we use server CPUs and GPUs; details are explained in Section 6.1 and in the Appendix.

### 1.3. Outline

In Chapter 2 we start off with explaining the environment for our research: while in disk-based DBMS most tasks were Input/Output (I/O) bound, Main Memory Database System (MMDBMS) make stored data available for the CPU with smaller latency and higher bandwidth. Hence, processing power has a higher impact in these systems and investigating other processing units makes more sense than before.

The most popular co-processor at the moment, the GPU, is explained in detail in Chapter 3. We start with the details about its architecture and the way it can be used by developers. With a series of benchmarks we give a first insight on how a GPU performs in certain categories compared to a CPU. Based on these findings we explain the further methodology of our work in Section 3.5. The terms *static* and *dynamic task* are explained there.

In Chapter 4 we take a deep look at candidates of three different classes of static tasks within a DBMS and explain how these algorithms work and perform on a GPU. While some application logic and query optimization can benefit from the GPU for certain input parameters, the maintenance task is not only data-intensive but also not "compatible" to the GPU's architecture. Even without the transfer bottleneck, the CPU would be faster and more efficient in processing.

However, the most important task of any DBMS is query execution, which we consider to be a dynamic task. Because of the GPU's characteristics we cannot use the approach of executing each database operator on its own as explained in Section 5.2. Instead we use the novel approach of generating code for each individual query and compile it at run-time. We present the approach, its advantages, especially for the GPU, as well as its limitations in Chapter 5.

Most tasks are not simply slower or faster on the GPU. Instead, it depends on the size of the input data and certain parameters that can only be determined at run-time. Because of the unlimited number of different situations and hardware-combinations we cannot decide at compile time, when to use which processing unit. The framework HyPE decides at run-time and is presented in Chapter 6.

# 2. Main Memory Database Management Systems

Relational Database Management Systems (RDBMSs) today have to serve a rich variety of purposes. From simple user-administration and profile storage in a web community forum to complex statistical analysis on costumer and sales data in world-wide acting corporations anything can be found. For a rough orientation the research community categorizes scenarios under two different terms: Online Transactional Processing (OLTP) and Online Analytical Processing (OLAP). Until recently there was no system that could serve both workloads efficiently. If a user wanted to do both types of queries on the same data, replication from one system to another was needed. Nowadays, the target of the major DBMS vendors is to tackle both types efficiently in one system. The bottleneck of I/O operations in traditional disk-based DBMS makes it impossible to achieve this goal.

The concept of the MMDBMS eliminates this bottleneck and gives the computational power of the processor a new higher priority. Because I/O operations are cheaper on Random Access Memory (RAM), processes that were I/O-bound in disk-based system are often CPU-bound in MMDBMS. Co-processor provide immense processing speeds for problems of their domain. Their integration into a MMDBMS is a new chance to gain better performance for such CPU-bound tasks.

In this chapter, we explain how MMDBMSs work and what possibilities and challenges arise because of their architecture. In the first section we explain the difference between OLTP and OLAP workloads, which is necessary for a basic understanding of the challenges DBMS researchers and vendors face. The following Section 2.2 explains the recent changes in hardware that explain the rising interest in MMDBMSs. We take a look at the architecture and techniques used in HANA to support both scenarios, so-called mixed workloads.

For this thesis we focus on the GPU as co-processor, but there are of course other candidates. Before we get to the details of GPUs in the next chapter, we take a look at noticeable attempts that were already made to integrate different types of co-processors into a DBMS in Section 2.3.

# 2.1. OLTP and OLAP

Based on characteristics and requirements for a DBMS there are two fundamentally different workloads: OLTP and OLAP.

A DBMS designed for OLTP must be able to achieve a high throughput of read and at the same time—write transactions. It must be able to keep the data in a consistent

#### 2. Main Memory Database Management Systems

state at every time and make sure that no data is lost even in case of a power failure or any other interruption. Additionally, transactions do not interfere in each others processing and are only visible, when they are completed successfully. These characteristics are know under the acronym ACID: Atomicity, Consistency, Isolation and Durability [41]. Users and applications that used RDBMSs rely on the system to act according to these rules. Typical Structured Query Language (SQL) statements of a OLTP workload are shown in Listing 2.1. They are a mixture of accessing data with simple filter criteria, updating existing tuples and the insertion of new records into the system.

#### Listing 2.1: Typical OLTP queries

```

1 SELECT * FROM customer

2 WHERE customer_id=12;

3

4 INSERT INTO customer(name, address, city, zip)

5 VALUES("Cust Inc", "Pay Road 5", "Billtown", 555);

6

7 UPDATE customer SET customer_status="gold"

8 WHERE name="Max Mustermann";

```

The requirements for a OLAP-optimized DBMS are different. Instead of simple and short transactions, they must support the fast execution of queries that analyze huge amounts of data. But in contrast to OLTP scenarios the stored data is not or only rarely changed. Therefore, the ACID rules do not play an important role in analytic scenarios. Compared to a OLTP scenario there are less queries, but every query accesses large amounts of data and usually involves much more calculations due to its complexity. A typical OLAP-query is shown in Listing 2.2.

Listing 2.2: Query 6 of the TPC-H benchmark [100]

```

1

SELECT sum(l_extendedprice * l_discount) as revenue

\mathbf{2}

FROM

lineitem

3

WHERE l_shipdate >= date ':1'

4

AND l_shipdate < date ':1' + interval

'1'

year

5

AND l_discount BETWEEN :2 - 0.01 AND :2

0.01

6

AND l_quantity < :3;

```

Although classic RDBMSs support OLTP and OLAP workloads, they are often not capable of providing an acceptable performance for analytical queries. Especially in enterprise scenarios another system is used that is optimized solely for OLAP. These so-called *data warehouses* use read-optimized data structures to provide fast access to the stored records. Furthermore, they are optimized to do calculations on/with the data while scanning it. Because the data structures used do not support fast changes, OLAP systems perform poorly at update- or write-intensive workloads. Therefore, the data that was recorded by the OLTP system(s) must be transferred regularly. This happens in form of batch inserts into the data warehouse. Since this process also involves some form

of transformation to read-optimized schemes and data structures, it is called Extract, Transform, Load (ETL) [102]. The batch insert can contain data from a high number of different system. Their exports are converted and may be pre-processed, e.g., sorted and aggregated, before they are actually imported into the OLAP system [58].

A typical business example that shows the organization of different DBMS, is a global supermarket chain. Every product that is sold has to be recorded. However, the transaction is not completed when the product is registered by the scanner at checkout, but when the receipt is printed. Until then it must be possible to cancel the transaction without any change to the inventory or the revenue. Additionally, in every store hundreds or thousands transaction are made every day. This is a typical OLTP workload for a DBMS. Similar scenarios can be found at a warehouse, where the goods are distributed to the stores in the region. Here, every incoming and outgoing product is recorded just in time. In contrast to that a typical OLAP-query is to find the store with the lowest profit of a certain region, or the product that creates the highest revenue in a month. This OLAP workload is usually handled by the data warehouse, which holds the records of all stores and warehouses.

This solution has disadvantages: since at least two DBMS are involved, there is no guarantee that data is consistent between both. During the ETL process, it must be ensured that no records are lost or duplicated. Additionally, because there is not one single source of truth, every query has to be executed in the right system. But the most significant disadvantage is that the more sources there are, the longer the ETL process takes. Hence, the time until the data is available for analysis gets longer, when more data is recorded. Especially in global companies *real-time analytics*<sup>1</sup> are not available with this approach [83].

### 2.2. Main Memory DBMS for a Mixed Workload

Most systems today use Hard Disk Drives (HDDs) as primary storage, because they provide huge amounts of memory at an affordable price. However, while CPU performance increased exponentially over the last years, HDD latency decreased and bandwidth increased only slowly. Table 2.1 lists the access latency of every memory type available in modern server hardware. There is a huge difference between HDD and RAM latency (and bandwidth as well), which is known as the *memory gap*. Therefore, the main performance bottleneck for DBMS nowadays (and at least in the last 20 years) is I/O. The first DBMSs that addressed this problem by holding all data in main memory while processing queries were available in the 1980s [26]. These MMDBMSs do not write intermediate results, e.g., joined tables, to disk like traditional disk-based system and therefore reduce I/O, especially for analytic queries, where intermediate results can become very large.

In recent years the amount of RAM fitting into a single machine passed the 1 TB mark and became cheap enough to replace the HDD in most business scenarios. Hence, the

<sup>&</sup>lt;sup>1</sup>This has of course nothing to do with the definition of *real-time* in computer science.

#### 2. Main Memory Database Management Systems

| L1 Cache                                        | $\approx 4$ cycles           |

|-------------------------------------------------|------------------------------|

| L2 Cache                                        | $\approx 10 \text{ cycles}$  |

| L3 Cache                                        | $\approx 40-75$ cycles       |

| L3 Cache via Intel QuickPath Interconnect (QPI) | $\approx 100-300$ cycles     |

| RAM                                             | $\approx 60  \mathrm{ns}$    |

| RAM via QPI                                     | $\approx 100  \mathrm{ns}$   |

| Solid State Drive (SSD)                         | $\approx 80000\mathrm{ns}$   |

| HDD                                             | $\approx 5000000\mathrm{ns}$ |

Table 2.1.: Approximation of latency for memory access (reads) [64, 30, 105]

concept of MMDBMS was extended to not only keep active data in main memory, but use RAM as primary storage for all data in the system<sup>2</sup>.

For DBMS vendors this poses a new challenge, because moving the primary storage to RAM means tuning data structures and algorithms for main memory characteristics and the second memory gap between CPU-caches and RAM. MMDBMS still need a persistent storage to prevent data loss in case of a power failure, therefore every transaction still triggers a write-to-disk operation. Hence, OLTP workloads can by principle not benefit as much as OLAP, but modern hardware enables these systems to provide acceptable performance for OLTP as well.

In the next sections we show some of the principle design decisions of relational MMDBMS on the example of SAP HANA. While other commercial RDBMS started of as disc-oriented systems and added main memory as primary storage in their products—e.g., SQLServer with Hekaton [20], DB2 with BLU [86], and Oracle with Times Ten [80]—HANA is built from the ground up to use main memory as the only primary storage.

#### 2.2.1. SAP HANA Architecture

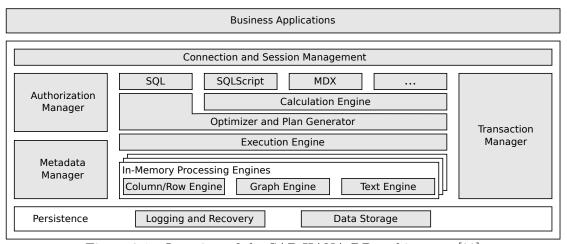

On the one hand SAP HANA is a standard RDBMS that supports pure SQL and, for better performance, keeps all data—intermediate results as well as stored data—in main memory. Hence, the system provides full transactional behavior while being optimized for analytical workloads. The design supports parallelization ranging from thread and core level up to distributed setups over multiple machines. On the other hand HANA is a platform for data processing specialized to the needs of SAP applications [21, 92, 22].

Figure 2.1 shows the general SAP HANA architecture. The core of the DBMS are the In-Memory Processing engines, where relational data can either be stored row-wise or column-wise. Data is usually stored in the column store, which is faster for OLAP scenarios as we will explain in Section 2.2.2. However, in case of clear OLTP workloads, HANA also provides a row store. The user of the system has to decide, where a table is stored at creation time, while the system handles the transfer between the storage engines when a query needs data from both. Hence, the ETL-process is not necessary,

<sup>&</sup>lt;sup>2</sup>To emphasize the difference SAP HANA is sometimes called In-Memory DBMS

#### 2.2. Main Memory DBMS for a Mixed Workload

Figure 2.1.: Overview of the SAP HANA DB architecture [22]

resp. transparent to the users of the DBMS. Psaroudakis et al. showed how HANA handles both types of workloads at the same time [85].

As a data management platform, HANA allows graph data and text data to be stored in two specialized engines next to relational data. In every case, processing and storage are focused on main memory. If necessary tables can be unloaded to disk, but have to be copied to main memory again for processing. Because of this there is no need to optimized data structures in any way for fast disk access. Instead data structures as well as algorithms are built to be cache-aware to cope with the second memory gap. Furthermore, the engines compress the data using a variety of compression schemes. As we discuss in Section 2.2.3 this not only allows more data to be kept in main memory but speeds up query execution as well.

Applications communicate with the DBMS with the help of various interfaces. Standard applications can use the SQL interface for generic data management functionality. Additionally, SQLScript [9] enables procedural aspects for data processing within the DBMS. More specialized languages for problems of a certain domain are MDX for processing data in OLAP cubes, WIPE to query graphs [90, 89], and even an R integration for statistics is available [39]. SQL queries are translated into an execution plan by the plan generator, which is then optimized and executed. Queries from other interfaces are eventually transformed into the same type of execution plan and executed in the same engine, but are first described by a more expressive abstract data flow model in the calculation engine. Independent of the interface, the execution engine handles the parallel execution and the distribution over several nodes.

On top of the interfaces there is the Component for Connection and Session Management, which is responsible for controlling individual connections between the database layer and the application layer. The authorization manager governs the user's permissions and the transaction manager implements snapshot isolation or weaker isolation levels. The metadata manager holds the information about where tables are stored in which form and on which machine if the system was set up in a distributed landscape. All data is kept in main memory, but to guarantee durability in case of an (unexpected)

#### 2. Main Memory Database Management Systems

Figure 2.2.: Row- vs. column-oriented storage

shutdown data needs to be stored on disk (HDD or SSD) as well. During savepoints and merge operations (see Section 2.2.4) tables are completely written to disk; in between updates are logged. In case of a system failure, these logs are replayed to recover the last committed state [22].

#### 2.2.2. Columnar Storage

Since relations are two-dimensional structures there has to be a form of mapping to store them in the one-dimensional address space of memory. In general there are two different forms: either relations are stored row-wise or column-wise.

As shown in Figure 2.2 in row-wise storage all values of a tuple are stored contiguously in memory. The most significant advantage is that the read access to a complete row as well the insertion of a new row, which often happens in OLTP scenarios, can be processed efficiently. In contrast column stores store all values of a column contiguously in memory. Therefore, access to a single row means collecting data from different positions in memory. In OLAP scenarios values of single attributes are regularly aggregated, which means that fast access to the whole column at once is beneficial. When queries access only a small number of columns in the table columnar storage allows to just ignore the other columns. Naturally, column stores have the advantage in these situations.

Main memory is still an order of magnitude more expensive than disk. Therefore, MMDBMSs use compression whenever possible before storing the data. In terms of compression, the columnar storage has an advantage: the information entropy of data stored within one column is lower than within one row. Every value is by definition of the same data type and similar to other values. Lower information entropy directly leads to better compression ratios [2]. It is easier, for instance, to compress a set of phone numbers than a set with a phone number, a name and an e-mail address. Additionally, often there is a default value that occurs in columns at a high frequency.

There are two different data layouts for column stores. MonetDB for instance uses the Decomposed Storage Model (DCM), which was first described by Copeland and Khoshafian [16]. Every value stored in the column gets an identifier to connect it with the other values of the same row, i.e., the row number of every value is explicitly stored. In MonetDB's Binary Association Table (BAT) structure, there are special compression schemes to minimize the overhead of storing this identifier, e.g., by just storing beginning and end of the range.

The second layout—which is used by HANA—stores every column of a table in the

same order, so that the position of a value inside the column automatically becomes the row identifier. While the overhead for the row identifier is not there in this layout, individual columns cannot be re-ordered, which often is advantageous for compression algorithms (cf. next Section).

#### 2.2.3. Compression

Compression in DBMSs is a major research topic. Not only does it save memory, it makes it also possible to gain performance by using compression algorithms that favor decompression performance over compression ratio [109, 1]. The reason is that, while we had an exponential rise in processing power for decades, memory bandwidth increased only slowly and latency for memory access, especially on disk, but also for main memory has been almost constant for years [83]. The exponential growth in processing power was possible because transistors became constantly smaller. Therefore the number of transistors per chip doubled every 18 months. This effect was predicted in the 1960s [69] and became know as Moore's law. While the number of transistors directly influences processing power and memory capacity, it does not necessarily affect memory latency and bandwidth, neither for disk nor for main memory. Hence, Moore's law cannot be applied to these characteristics. There was some growth in bandwidth (for sequential access!) but especially seek times for hard disks have not changed in years because they are limited by mechanical components. Main memory development was also slower than the CPU's.

Therefore, even in MMDBMS I/O to main memory is the bottleneck in many cases, e.g., scanning a column while applying filter predicates is memory bound even with compression [103]. Modern multi-core CPUs are just faster at processing the data than reading it from memory. By using compression algorithms we do not only keep the memory footprint small, we also accelerate query performance. This is of course only true for read-only queries, not for updates. Updates on compressed structures are a major problem, because they involve decompression, updating de-compressed data and re-compression of the structure. To prevent this process happening every time a value is update, they are usually buffered and applied in batches. We describe the details of this process in Section 2.2.4.

In HANA's column store different compression schemes are used on top of each other. We describe the most important ones in the following paragraphs.

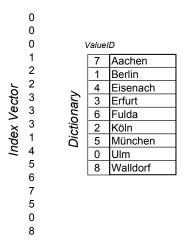

#### **Dictionary Encoding**

A very common approach to achieve compression in column stores is dictionary or domain encoding. Every column consists of two data structures as depicted in Figure 2.3: a dictionary consisting of every value that occurs at least once in the column and an *index vector*. The index vector represents the column but stores references to the dictionary entries, so called *value IDs*, instead of the actual values.

In many cases the number of distinct values in one column is small compared to the number of entries in this column. In these cases the compression ratio can be immense.

#### 2. Main Memory Database Management Systems

Figure 2.3.: Dictionary compression on the example of a city column

For typical comment columns or alike, in which almost every value is unique, there is mostly no effect on the memory footprint. If every value is distinct, even more space is needed.

Although numeric columns do not benefit from this type of compression in terms of memory usage, HANA stores all regular columns in dictionary encoded form. There are various reasons for that, e.g., the execution of some query types can be done more efficiently with the help of the dictionary. Obviously distinct queries can be answered by just returning the dictionary. Also, query plans for SQL-queries with a group by clause for example can be optimized better because the maximum number of rows in the result can be easily calculated because the size of the dictionary is known. But the most important reason for dictionary encoding is that compression techniques for the index vector can be applied independently of the type of the column.

#### **Bit-Compression for Index Vectors**

In combination with dictionary encoding the most efficient compression algorithm for the index vector is bit-compression. Usually the value IDs would be stored in a native, fixed-width type such as *integer* (or *unsigned integer*), i.e., every value ID needs 32 bit. Since we know the maximum value ID  $v_{max}$  that occurs in the index vector—the size of the dictionary—we also know that all value IDs fit into  $n = \lceil \log_2 v_{max} \rceil$  bit. Hence, we can just leave out the leading zeros, which makes bit-compression a special form of prefix-compression. With this approach we do not only achieve a high compression ratio in most scenarios, but we also gain scan performance. Because we are memory bound while scanning an uncompressed column and the de-compression of bit-compressed data can be implemented very efficiently with SIMD-instructions, the scan throughput is higher with compression [104, 103] than without. Moreover, bit-compression allows the evaluation of most predicates, e.g., the where-clause of SQL-statements, on-the-fly without de-compressing the value IDs. The performance depends strongly on the bitcase, i.e., the size of one value ID in memory, but even with complex predicates we are still memory-bound when scanning with one thread only [103].

In contrast to the other compression techniques shown here, bit-compressed data can never be greater than the uncompressed value IDs. The only draw-back of this form of compression is that the direct access to a single value requires the decompression of one block of values. In most cases, however, the initial cache-miss dominates the access time. Therefore, similar to dictionary encoding this type of compression is used for every stored index vector in HANA.

#### Further Light-Weight Compression (LWC) Techniques

Additionally there are other forms of compression techniques used within HANA. One of the major requirements is that compressed data can be de-compressed fast while scanning and also while accessing single values, i.e., they are light-weight. Sophisticated algorithms, such as bzip2 or LZMA usually achieve a better compression ratio, but are just too slow for query execution. While most of the LWC-techniques work well for sequential scanning of a column, access times for single values vary.

In Figure 2.4 the used techniques for compression in HANA to date are depicted. They are explained in detail in [63].

*Prefix coding* eliminates the first values of the index vector when they are repeated. In most columns there is no great benefit to use it, except for sorted columns. However, this compression type introduces almost no overhead and does not affect scan performance. Therefore, it is often combined with other techniques.

Sparse coding works by removing the most frequent value IDs from the index vector and managing an additional bit vector, where the positions of removed value IDs are marked. Especially the default value often occurs in columns, therefore this algorithm achieves a good compression ratio in most cases. A disadvantage is that direct access requires the calculation of the value ID's position in the compressed index vector by building the prefix sum of the bit vector. Depending on the position of the requested value ID this leads to a large overhead compared to the simple access.

Run-length encoding (RLE) (slightly modified version of [32]) compresses sequences of repeating value IDs by only storing the first value of every sequence in the index vector and the start of each sequence in another vector, which can also be bit-compressed. While this may achieve good compression ratios for columns, where values are clustered, there is the possibility that the compressed structure may need even more memory than the uncompressed index vector. Single access to a value ID at a given position requires a binary search in the vector that holds the starting positions and can therefore be expensive.

For *cluster coding* the index vector is logically split into clusters with a fixed number of value IDs. If one partition holds only equal value IDs, it is compressed to a single value ID. A bit vector stores whether the partition is compressed or not. Similar to RLE this achieves good ratios for clustered values, but the compression is limited by the chosen cluster size. Like with sparse coding a single lookup requires the calculation of the prefix sum for the bit vector and can therefore be expensive. Cluster coding can

|       |         | Prefix Coding |    |

|-------|---------|---------------|----|

| Uncor | npresse | ed            |    |

| IV    | Pos     |               |    |

| 0     | 0       |               | IV |

| 0     | 1       |               | 1  |

| 0     | 2       | <i>a</i> .    | 1  |

| 1     | 3       | prefix value: | 2  |

| 2     | 4       | 0             | 2  |

| 2     | 5       |               | 3  |

| 3     | 6       | prefix count: | 3  |

|       | -       | 3             | 3  |

| 3     | 7       |               | 0  |

| 3     | 8       |               | -  |

| 0     | 9       |               |    |

|       |         |               |    |

# Sparse Coding

| Uncompressed                    |                                           |                                               |                             |  |  |  |  |  |  |

|---------------------------------|-------------------------------------------|-----------------------------------------------|-----------------------------|--|--|--|--|--|--|

| IV                              | Pos                                       |                                               |                             |  |  |  |  |  |  |

| 0<br>0<br>1<br>2<br>3<br>3<br>3 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | sparse value:<br>0<br>Bitvector:<br>111000001 | IV<br>1<br>2<br>3<br>3<br>3 |  |  |  |  |  |  |

| 0                               | 9                                         |                                               |                             |  |  |  |  |  |  |

# Run Length Coding

# **Cluster Coding**

| Uncor                                | npressed                                       |                        |                             | Uncol                                     | mpressed                                       | 1                                        |                             |

|--------------------------------------|------------------------------------------------|------------------------|-----------------------------|-------------------------------------------|------------------------------------------------|------------------------------------------|-----------------------------|

| IV                                   | Pos                                            |                        |                             | IV                                        | Pos                                            |                                          |                             |

| 0<br>0<br>1<br>2<br>3<br>3<br>3<br>0 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | RLE Start<br>0 3 4 6 9 | IV<br>0<br>1<br>2<br>3<br>0 | 0<br>0<br>1<br>2<br>3<br>3<br>3<br>3<br>0 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | cluster size:<br>3<br>Bitvector:<br>1010 | IV<br>0<br>1<br>2<br>3<br>0 |

Figure 2.4.: Compression algorithms for the index vector

be extended to *indirect coding* by creating a dictionary for a cluster that contains more than one value ID.

Except for prefix compression the direct access to the value ID at a given position gets more expensive the larger the index vector gets. To limit the time needed for such an access, every compression is applied to blocks of values with a fixed size. This way every single lookup requires to calculate the right block number and the access to the structure that stores the compression technique for this block. Afterwards, the block needs to be de-compressed to access the value. The block-wise approach also has the advantage that the best compression algorithm can be chosen for parts of the index vector. Overall this gives a better compression ratio than using one technique for the complete column [63].

#### **Re-Ordering Columns for Better Compression Ratios**

All compression techniques shown in the last section do work best for columns that are sorted by the frequency of their value IDs. Especially having the most frequent value ID on top is the best situation in every case, because we can combine all techniques with prefix-coding (of course this is not necessary for RLE). Fortunately, relations do not guarantee any order. Therefore, HANA is free to re-arrange the rows to gain better performance or a smaller memory footprint. Of course, the columns cannot be sorted independently since this would require to map the row number to the position of a value ID. In most cases this would be more expensive (in terms of memory footprint and compression) than having no LWC at all. Hence, the system has to determine which column it sorts for a good performance. Finding the optimal solution for this problem is NP-complete [5]. Lemke et al [63] propose greedy heuristics to find a near-optimal solution. The key to finding a good solution is a combination of only considering columns with small dictionaries and applying the compression techniques to samples of each of these columns.

#### **Compression of String Dictionaries**

In typical business scenarios up to 50% of the total databases size are the dictionaries of string columns [87]. In many cases the largest of these dictionaries are the ones that are accesses rarely. In the TPC-H benchmark the *comment* column of the *lineitem* table is a typical example [100]. While it is the largest of all columns—uncompressed it is one fourth of the whole database size—there is no query that accesses it. The *comment* column of the *orders* table, one eighth of the total, is accessed in one of the 22 queries of the benchmark. The compression of these dictionaries is therefore essential to bring the memory footprint down, while there is no impact on the performance in many cases. Hence, in contrast to index vectors, it can also make sense to use heavy-weight compression on some string dictionaries. But the candidates have to be carefully chosen, since access to certain dictionaries may be performance critical. Ratsch [87] evaluates known compression schemes for string dictionaries in HANA and compares there suitability for common benchmarks. He achieves compression rates between 30% and 50% without a significant impact on the scan-performance. However, the time

#### 2. Main Memory Database Management Systems

needed for initially compressing the dictionaries has to be considered as well. The work shows that automatically determining the right scheme is a complicated task and cannot be done without access statistics and sample queries on the compressed data.

#### 2.2.4. Main and Delta Storage

Although the compression techniques presented in the last section have different characteristics in terms of compression ratios, scan-, and single-lookup-performance, they have one thing in common: they have a noticeable impact on the write-performance. In many cases the update of a single value triggers the de- and re-compression of the whole structure that holds the column. The insertion of one row into a large table might take seconds, especially with all the algorithms that are executed to evaluate the optimal compression scheme for parts of the table. This therefore contradicts the original goal of building HANA as a MMDBMS to support mixed-workloads.

Since column stores have a poor write performance in general because of the memory layout, this is a common problem. The general idea is to buffer updates in a secondary data structure, while keeping the main storage static. C-Store [98], for instance, differentiates between *Read-optimized Store (RS)* and *Writeable Store (WS)* [94]. A so called *Tuple Mover* transfers data in batches from WS to RS.

HANA's update buffer, called *Delta Storage*, is optimized to keep read- and writeperformance in balance. It stores data in columns just like the main storage, but because it usually holds less data than the main storage, none of the compression techniques, except for dictionary encoding, are used. The delta dictionary is independent of the main dictionary, i.e., values may appear in both dictionaries with different value IDs. In consequence a insertion operation only triggers a lookup in the delta dictionary. In case the value is already there, the value ID is inserted into the column. If the value is not in the column, it is inserted and a new value ID is assigned. While the main dictionary is stored as a sorted array, where the value ID is the position of a value inside the array, the delta dictionary has to use a structure which consists of two parts to provide fast look-ups and insertions. First, values are stored in an array in order of their insertions. The value ID is the position of the of the value within the array. However, finding the value ID belonging to a value takes  $\mathcal{O}(n)$  operations. Therefore, values are also inserted in a B+-Tree, where they are used as key and the value ID is the (tree-)value. This way, the value ID belonging to a value can be found with  $\mathcal{O}(\log n)$  operations. Insertions have the same complexity.

HANA uses an insert-only approach, i.e., update operations delete the old entry and insert a new one. Because removing the row from main storage immediately would be expensive, it is marked invalid in a special bit-vector instead and finally removed when the delta is merged into the main storage. HANA also supports temporal data, then the bit-vector is replace with two time stamps that mark the time range for which the entry was valid [55].

With the delta approach the main storage can be optimized solely for reading and it can be stored on HDDs as is to guarantee durability. In contrast the delta storage is kept only in main memory, but operations are logged to disk. In case of a a system failure, the main storage can simply be loaded and the delta log has to be replayed to return to the last commited state. Of course data has to be moved from delta buffer to main storage at some point in time. This process—called Delta Merge—creates a new main dictionary with entries from the old main and delta dictionary. Afterwards all value IDs have to be adjusted to the new dictionary. This can be done without look-ups in the new dictionary by creating a mapping from old to new IDs while merging the dictionaries. During the whole operation all write transactions are redirected to a new delta buffer, read transaction have to access the old main and delta as well as the new delta storage. Except for the short time, when the new delta and main are activated, there is no locking required. In Section 4.3 we take a closer look at the creation of the new dictionary.

## 2.3. Related Work: Using Co-processors in a DBMS

Before we focus on GPUs for the remainder of this thesis, we take a look at related work that concentrates on other available co-processors in the context of DBMS.

FPGAs are versatile vector processors that provide a high throughput. Müller and Teubner provide an overview of how and where FPGAs can be used to speed up DBMS in [70]. One of there core messages is that an FPGA can speed up certain operations but should—like the GPU—be used as a co-processor next to the CPU. In [97] the same authors present a concrete use case: doing a stream join on the FPGA.

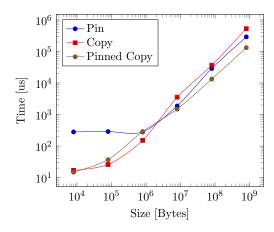

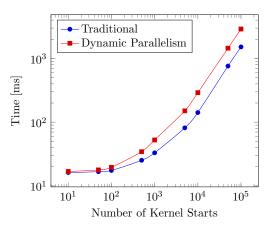

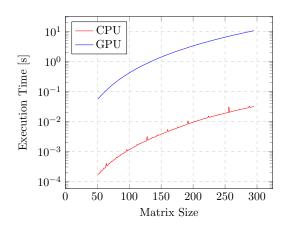

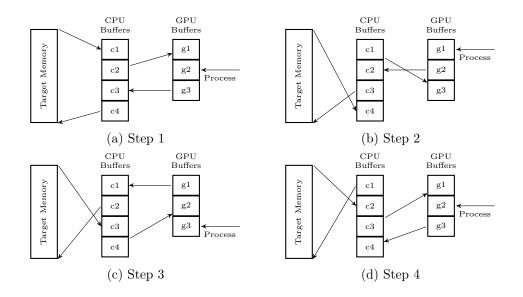

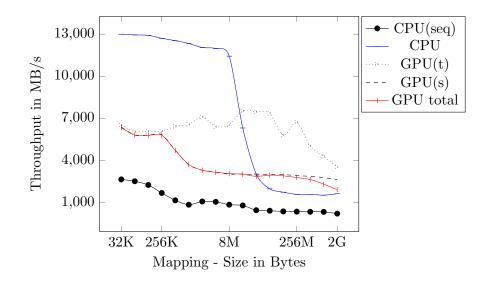

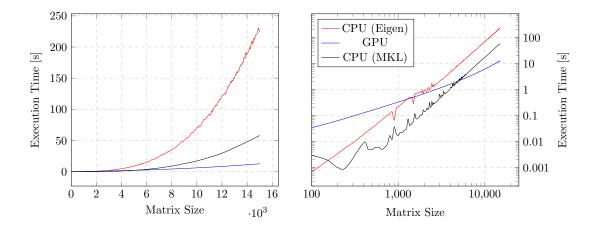

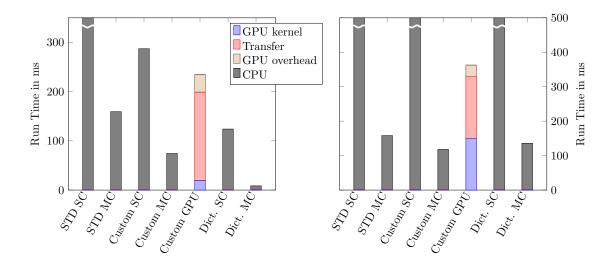

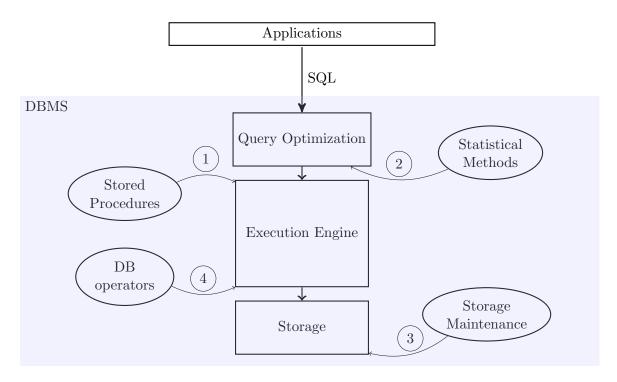

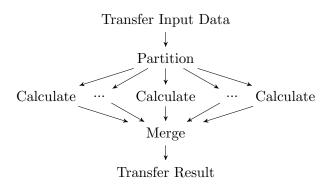

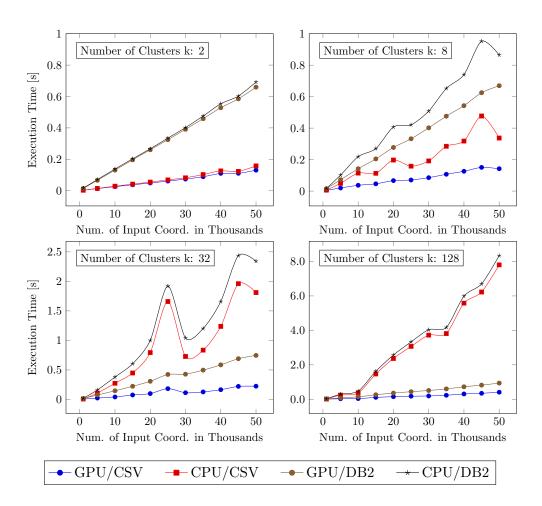

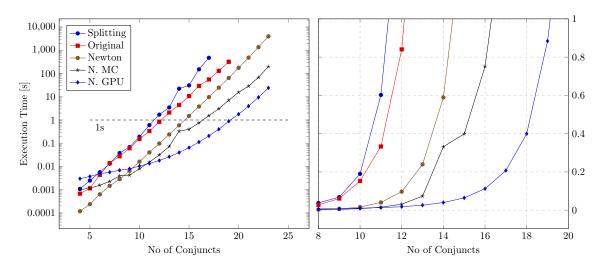

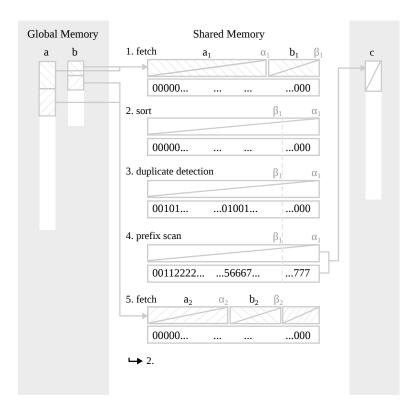

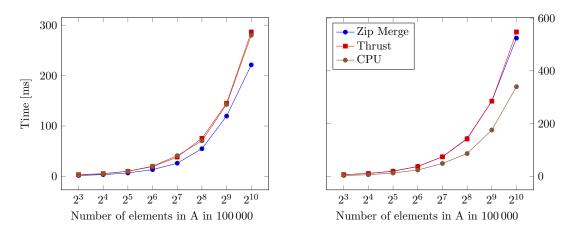

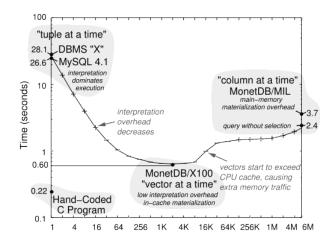

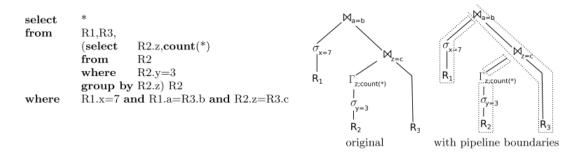

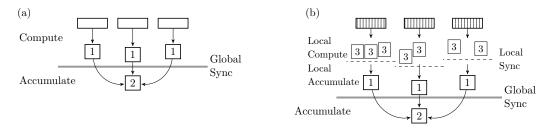

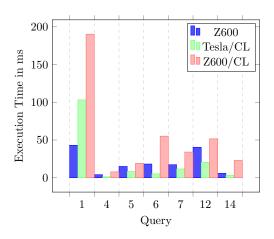

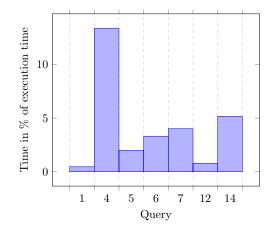

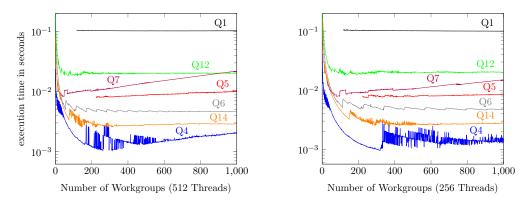

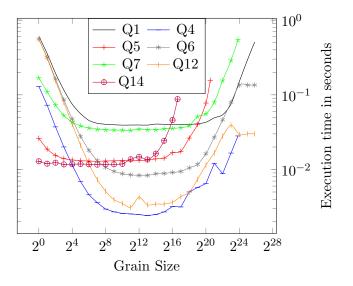

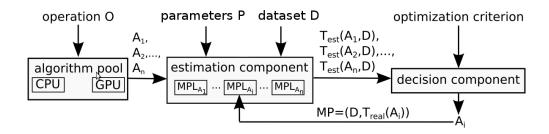

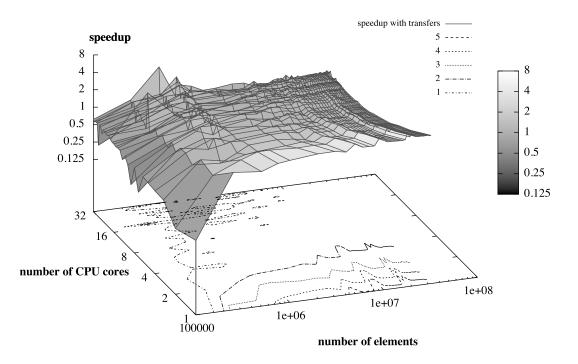

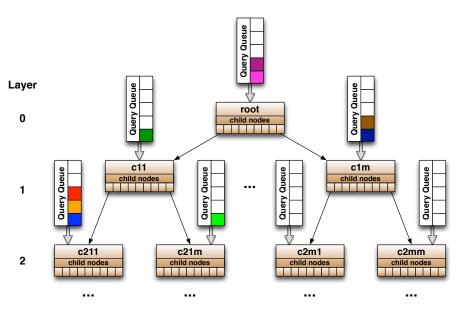

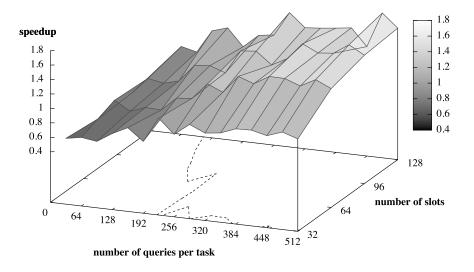

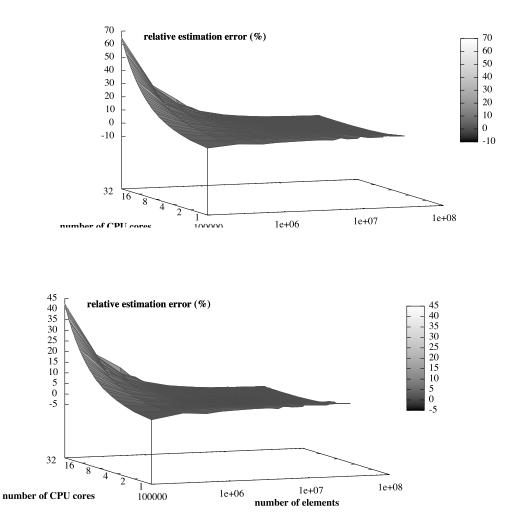

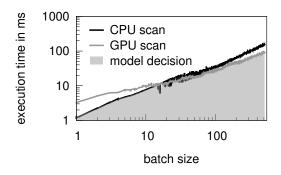

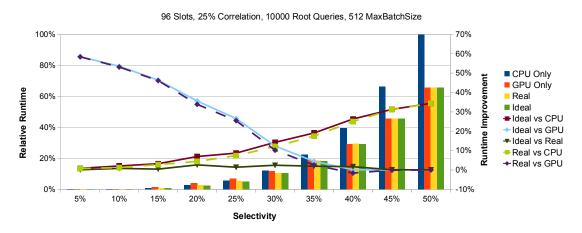

The stream join was also evaluated on the cell processor in [29, 28]. However, the cell processor is not a typical co-processor but a heterogeneous platform that provides different types of processing units, the PowerPC Processing Element (PPE) and 8 Synergistic Processing Elements (SPEs). The PPE is similar to a typical CPU core, while the SPEs work together like a vector machine. The co-processing concept is inherent in this architecture, because the developer has to decide which processing unit to use for every algorithm. We will face similar challenges in the future with heterogeneous architectures that provide CPU and GPU on the same chip. The same authors also published work about sorting on the cell processor [27].